FPGA是什么。

我怎么知道。

FPGA中流水线并行

FPGA中流水线并行指的是什么,与GPU,CPU有什么本质区别

简单地说

处理一个数据包有10个步骤,FPGA可以搭建一个10级流水线,流水线的不同级在处理不同的数据包,每个数据包流经10级之后处理完成。每个处理完成的数据包可以马上输出。而GPU的数据并行方法是做10个计算单元,每个计算单元也在处理不同的数据包,但是所有的计算单元必须按照统一的步调,做相同的事情(SIMD)。这就要求10个数据包必须同进同出。当任务是逐个而非成批到达的时候,流水线并行比数据并行可实现更低的延迟。因此对流水式计算的任务,FPGA比GPU天生有延迟方面的优势。

详细表述

以下内容来自:

source: CPU,GPU和FPGA的计算体系结构比较

source: 怎么理解SIMD和SIMT

CPU架构

当没有依赖关系时,标量流水线型CPU内核可以按每个时钟周期(IPC)最多一条指令的速率执行分为几级的指令。为了提高性能,现代CPU内核是具有复杂机制的多线程超标量处理器,这些机制用于查找指令级并行性并在每个时钟周期执行多个乱序指令。他们一次获取许多指令,找到这些指令的依赖图,利用复杂的分支预测机制,然后并行执行这些指令(就IPC而言,通常是标量处理器性能的10倍)。

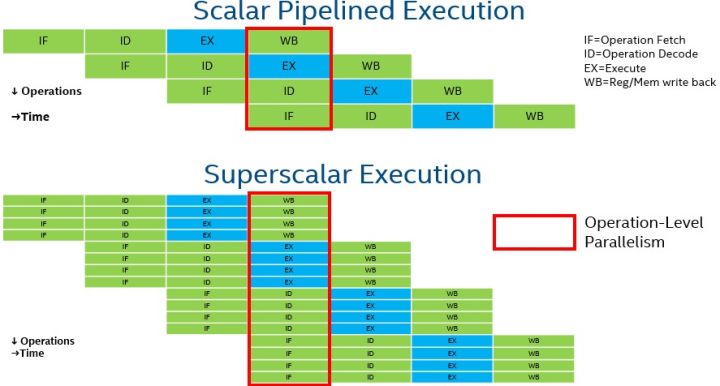

如下图,CPU流水线与超量流水线的简化示意图:

- 由于直接使用CPU运行不需要把数据卸载到协处理器(如GPU和FPGA),因此数据传输开销是最小的,减小了数据处理的等待时间。

- 同时,由于大部分软件的算法本质上都是串行的,不需要并行流水线,因此直接采用CPU也可以达到高性能。

- 对于可以矢量并行化的算法部分,现代CPU支持单指令,多数据(SIMD)指令,例如英特尔®高级矢量扩展512。

- 因此,CPU适合各种工作负载。即使对于大量并行工作负载,对于具有高分支散度或高指令级并行度的算法,CPU的性能也要优于加速器,尤其是在数据大小与计算比很高的情况下。

CPU优势:

- 无序超标量执行

- 复杂的控制可提取巨大的指令级并行度

- 准确的分支预测

- 顺序代码上的自动并行

- 大量受支持的指令

- 与卸载加速相比,延迟更短

- 顺序执行代码可简化开发过程

GPU架构

GPU是由大规模并行,更小,更专业的内核构成的处理器,而这些处理器通常比高性能CPU中的内核更强大。GPU体系结构针对所有内核的总吞吐量进行了优化,从而不再强调各个线程的延迟和性能。GPU体系结构有效地处理矢量数据(数字数组),通常称为矢量体系结构。

GPU专用于计算的硅空间更多,而用于缓存和控制的硅空间则更少。结果,GPU硬件探索了较少的指令级并行性,并依靠软件提供的并行性来实现性能和效率。

GPU是有序处理器,不支持复杂的分支预测。相反,它们具有过多的算术逻辑单元(ALU)和深层流水线。通过大型独立数据的多线程执行来实现性能,这将分摊更简单的控制和更小的缓存的成本。

GPU采用单指令多线程(SIMT)执行模型,其中多线程和SIMD一起使用。在SIMT模型中,多个线程(工作项或SIMD通道操作序列)在同一SIMD指令流中以锁步方式进行处理。多个SIMD指令流映射到单个执行单元(EU),并且当一个流停止时,GPU EU可以在这些SIMD指令流之间进行上下文切换。

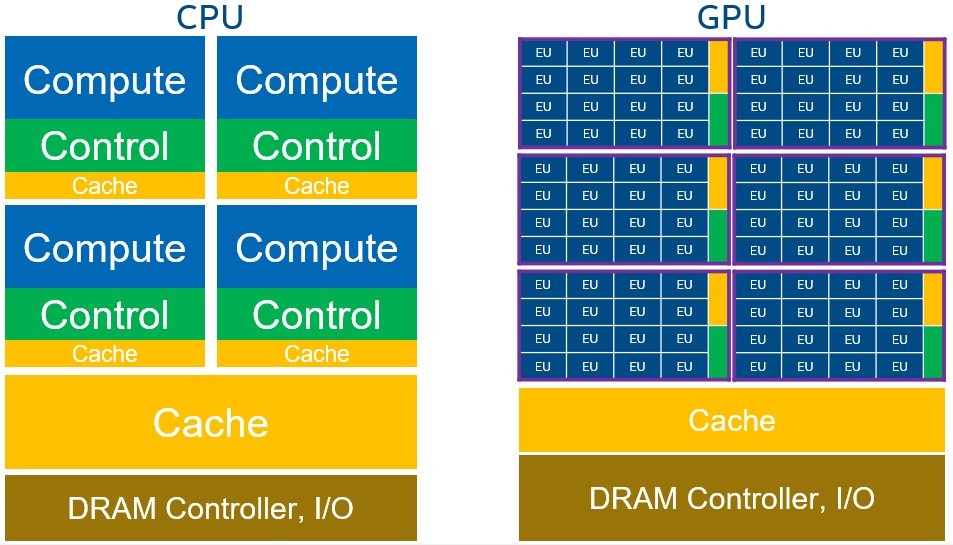

上图显示了CPU和GPU之间的区别。EU是GPU上处理的基本单位。每个EU可以处理多个SIMD指令流。在相同的硅空间中,GPU比CPU具有更多的内核/ EU。GPU是按层次结构组织的。多个EU组合在一起,形成具有共享本地内存和同步机制(又名子切片或流式多处理器,以紫色概述)的计算单元。计算单元组合形成GPU。

GPU优势:

- 大规模并行,多达数千个小型高效SIMD内核/ EU

- 高效执行数据并行代码

- 高动态随机存取存储器(DRAM)带宽

FPGA架构

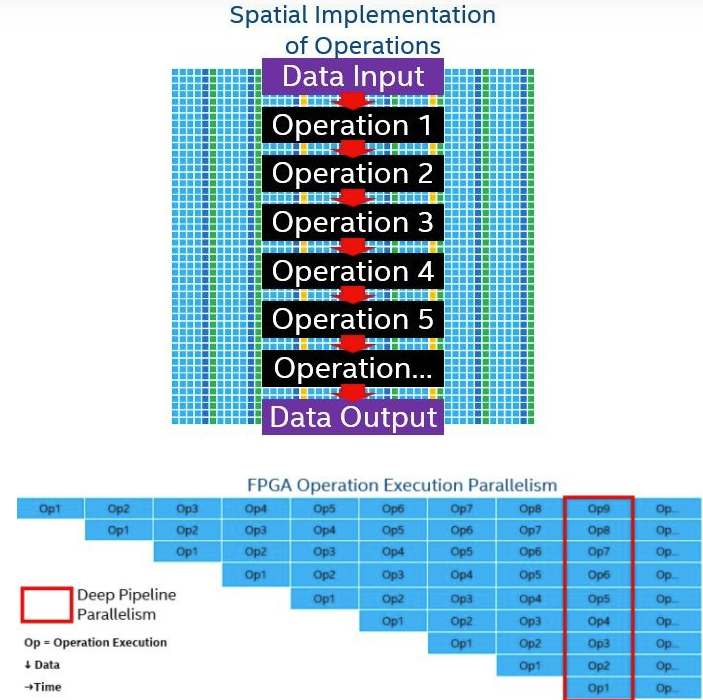

与可以通过软件编程的固定架构的CPU和GPU不同,FPGA是可重新配置的,其计算引擎由用户定义。当编写针对FPGA的软件时,已编译的指令成为硬件组件,这些组件在空间上排列在FPGA架构上,并且这些组件都可以并行执行。因此,FPGA体系结构有时被称为空间体系结构。

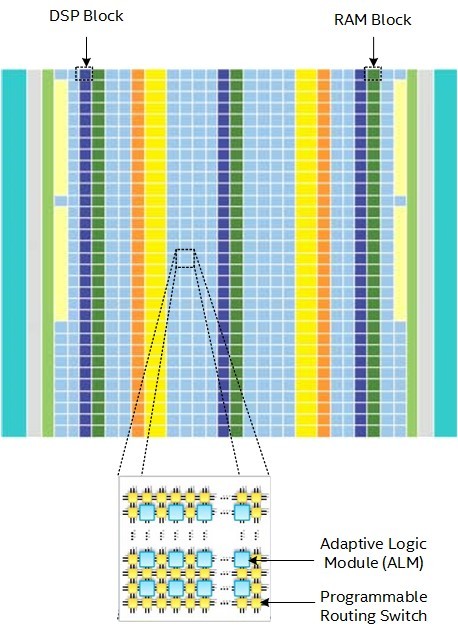

FPGA是由大量小型处理单元组成的阵列,其中包含多达数百万个可编程的1位自适应逻辑模块(每个模块都可以像一个位的ALU一样工作),多达数万个可配置的存储块以及成千上万个数学引擎,称为数字信号处理(DSP)块,支持可变精度浮点和定点运算。所有这些资源都是通过可根据需要激活的可编程导线网格连接的。

在FPGA上“执行”软件时,其执行方式与在CPU和GPU上执行已编译和汇编的指令的意义不同。取而代之的是,数据流经过与软件中表达的操作相匹配的FPGA上定制的深层流水线。由于数据流管道硬件与软件匹配,因此消除了控制开销,从而提高了性能和效率。使用CPU和GPU,指令级流水线化,新指令在每个时钟周期开始执行。使用FPGA,操作流水线化,因此对不同数据进行操作的新指令流将在每个时钟周期开始执行。

也就是说,即使CPU和GPU采用SIMD,操作还是要跟着指令流程走,当前指令流程未走完不能开启新的流程。而FPGA每个时钟周期都可以开始一个新的指令流程。

尽管管线并行化是FPGA并行化的主要形式,但它可以与其他类型的并行化结合使用。例如,可以将数据并行性(SIMD),任务并行性(多个流水线)和超标量执行(并行执行的多个独立指令)与流水线并行性一起使用,以实现最佳性能。

FPGA的优势:

- 效率:数据处理管道完全根据软件需求进行调整。无需控制单元,指令获取单元,寄存器写回和其他执行开销。

- 定制指令:CPU / GPU本身不支持的指令可以在FPGA上轻松实现并有效执行(例如,位操作)。

- 可以解决跨并行工作的数据依赖性,而不会导致流水线停滞。

- 灵活性:可以重新配置FPGA,以适应不同的功能和数据类型,包括非标准数据类型。

- 定制的片上存储器拓扑已调整为算法:内置大带宽的片上存储器以适应访问模式,以最大程度地减少或消除停顿。

- 丰富的I / O:FPGA内核可以直接与各种网络,内存以及自定义接口和协议进行交互,从而实现了低确定性的延迟解决方案。

SIMT(Single Instruction Multiple Thread)

单指令多线程,一般在CPU和GPU中采用这种模式。

简单举个例子描述:

假设有两个等长的数组,需要每个元素一一对应相加。那么SIMT的思想就是给每个元素分配一个线程,那么一个线程只需要完成一个元素的加法,所有线程并发(Concurrent)执行完成后,两个数组的相加就完成了。

从结构上来讲,一个多核系统,每个核有它自己的寄存器文件,有它自己的ALU(可能支持SIMD),有它自己的数据Cache,但是它只有一个Program Counter寄存器,一个指令Cache和一个译码器,指令被同时广播给所有的SIMT核。每个SIMT核有它自己独立的栈和数据集。

SIMT的好处是无需开发者费力把数据凑成合适的矢量长度,并且SIMT允许每个线程有不同的分支。 纯粹使用SIMD不能并行的执行有条件跳转的函数,很显然条件跳转会根据输入数据不同在不同的线程中有不同表现,这个只有利用SIMT才能做到。(虽然如此,但是SIMT采用分支条件的算法也会大幅度降低性能)

SIMD(Single Instruction Multiple Data)

顾名思义,单指令多数据,即在一条指令完成多个数据的计算。比如,通常一次加法操作只能完成一个整数的加法,而通过SIMD指令,一个次加法可以完成多个整数的加法。这就需要增加硬件ALU单元的数量,同时也需要增加同一个功能单元的数据通路数量,这样就能够增加一个时钟周期的吞吐量。

再说的白话一些就是,假如我们有两个相同元素个数的数组,想把两个数组元素一一对应相加。在SISD指令中只有一个ALU,我们需要用for循环一个一个元素进行相加,但在SIMD指令中,我们就不需要for循环,可以给每个元素分配一个ALU(假设有足够的ALU),那么这就是SIMD。

与SIMT相比的不同一点在于SIMD中的向量中的元素相互之间可以自由通信,因为它们存在于相同的地址空间(例如,都在CPU的同一寄存器中),而SIMT中的每个线程的寄存器都是私有的,线程之间只能通过shared memory和同步机制进行通信。

简而言之,SIMD提供了硬件级的并发支持,对于单纯计算的指令并发有着较好较高的效率。

而SIMT则更加灵活,允许有条件分支的存在,对数据的处理也更加方便。

相同点都是只有当前指令流结束了才可以开启下一个指令流。(因为PC共用)

计算密集型/通信密集型

计算密集型/通信密集型指的是什么,什么样的任务更适用于FPGA,而不是GPU

计算密集型

1、特点:要进行大量的计算,消耗CPU资源。比如计算圆周率、对视频进行高清解码等等,全靠CPU的运算能力。

2、计算密集型任务虽然也可以用多任务完成,但是任务越多,花在任务切换的时间就越多,CPU执行任务的效率就越低,所以,要最高效地利用CPU,计算密集型任务同时进行的数量应当等于CPU的核心数。

3、计算密集型任务由于主要消耗CPU资源,因此,代码运行效率至关重要。Python这样的脚本语言运行效率很低,完全不适合计算密集型任务。对于计算密集型任务,最好用C语言编写。

计算密集型任务的例子包括矩阵运算、图像处理、机器学习、压缩、非对称加密、Bing 搜索的排序等。

通信密集型

对称加密、防火墙、网络虚拟化都是通信密集型的例子。

GPU VS FPGA (机器学习为例)

source:

服务器端人工智能,FPGA和GPU到底谁更强?

主要从以下几个指标来对比GPU和FPGA:

- 峰值性能

- 灵活性

- 平均性能

- 功耗和能效比

峰值性能

GPU(10Tflops)远远高于FPGA(<1TFlops)。

这是由于GPU的架构经过仔细设计(例如使用深度流水线,retiming等技巧),在电路实现上是基于标准单元库而在关键路径(即芯片中一个时钟周期内延迟最长的路径,直接决定了电路最高运行速度)上可以用手工定制电路,甚至在必要的情形下可以让半导体fab依据设计需求微调工艺制程,因此可以让许多core同时跑在非常高的频率。

相对而言,FPGA首先设计资源受到很大的限制,例如GPU如果想多加几个core只要增加芯片面积就行,但FPGA一旦你型号选定了逻辑资源上限就确定了(浮点运算在FPGA里会占用很多资源)。而且,FPGA里面的逻辑单元是基于SRAM-查找表,其性能会比GPU里面的标准逻辑单元差好多。最后,FPGA的布线资源也受限制(有些线必须要绕很远),不像GPU这样走ASIC flow可以随意布线,这也会限制性能。

除了芯片性能外,GPU相对于FPGA还有一个优势就是内存接口。GPU的内存接口(传统的GDDR5,最近更是用上了HBM和HBM2)的带宽远好于FPGA的传统DDR接口(大约带宽高4-5倍),而众所周知服务器端机器学习算法需要频繁访问内存,因此内存接口的带宽可以决定机器学习应用的性能。

灵活性

从灵活性来说,FPGA远好于GPU。

FPGA可以根据特定的应用去编程硬件(例如如果应用里面的加法运算非常多就可以把大量的逻辑资源去实现加法器),但是GPU一旦设计完那就没法改动了,没法根据应用去调整硬件资源。

目前机器学习大多数适合使用SIMD架构(即只需一条指令可以平行处理大量数据),因此用GPU很适合。但是有些应用是MISD(即单一数据需要用许多条指令平行处理),这种情况下用FPGA做一个MISD的架构就会比GPU有优势。

平均性能

综上,由于GPU的峰值远高于FPGA的峰值性能,因此平均性能上FPGA只能依靠架构优势。即对于平均性能,看的就是FPGA加速器架构上的优势是否能弥补运行速度上的劣势。如果FPGA上的架构优化可以带来相比GPU架构两到三个数量级的优势,那么FPGA在平均性能上会好于GPU。

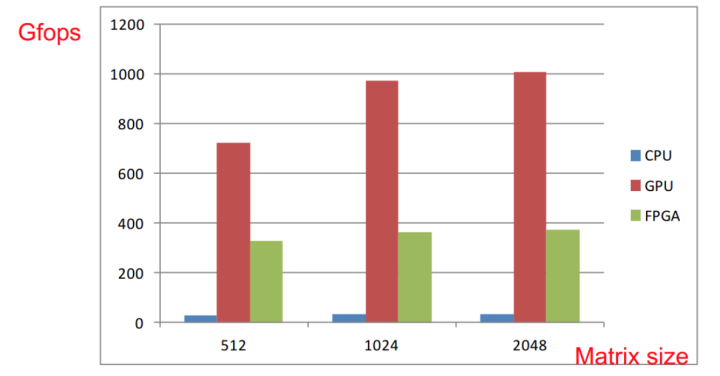

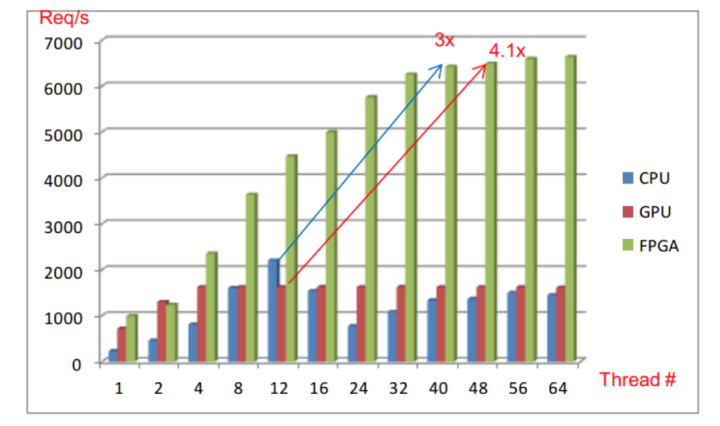

例如,百度在HotChips上发布的paper显示,GPU的平均性能相比FPGA在矩阵运算等标准batch data SIMD bench上远好于FPGA;但是在处理服务器端的少量多次处理请求(即频繁请求但每次请求的数据量和计算量都不大)的场合下,平均性能会比GPU更好。

Baidu的研究显示,对于矩阵运算bench GPU远好于FPGA,但是当处理小计算量大批次的实际计算时FPGA性能优于GPU。

功耗

与平均性能一样,这一点也要看具体的架构设计情况。

虽然GPU的功耗(200W)远大于FPGA的功耗(10W),但是如果要比较功耗应该比较在执行效率相同时需要的功耗。

如果FPGA的架构优化能做到很好以致于一块FPGA的平均性能能接近一块GPU,那么FPGA方案的总功耗远小于GPU,散热问题可以大大减轻。反之,如果需要二十块FPGA才能实现一块GPU的平均性能,那么FPGA在功耗方面并没有优势。

能效比的比较也是类似,能效指的是完成程序执行消耗的能量,而能量消耗等于功耗乘以程序执行的时间。虽然GPU的功耗远大于FPGA的功耗,但是如果FPGA执行相同程序需要的时间比GPU长几十倍,那FPGA在能效比上就没有优势了;反之如果FPGA上实现的硬件架构优化得很适合特定的机器学习应用,执行算法所需的时间仅仅是GPU的几倍或甚至于接近GPU,那么FPGA的能效比就会比GPU强。