麻。

第一章 开关理论基础

1.1 二进制系统

两种基本的二进制表现波形:电平型和脉冲型

- 电平型:一般用于数据信号,高低电平表示1/0

- 脉冲型:一般用于控制信号,上升沿或者下降沿有效

1.2 数制和码制

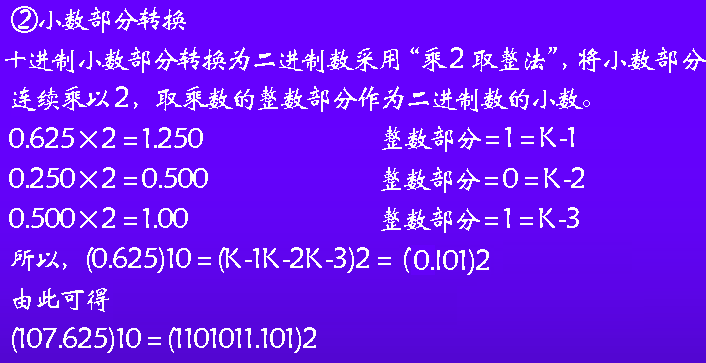

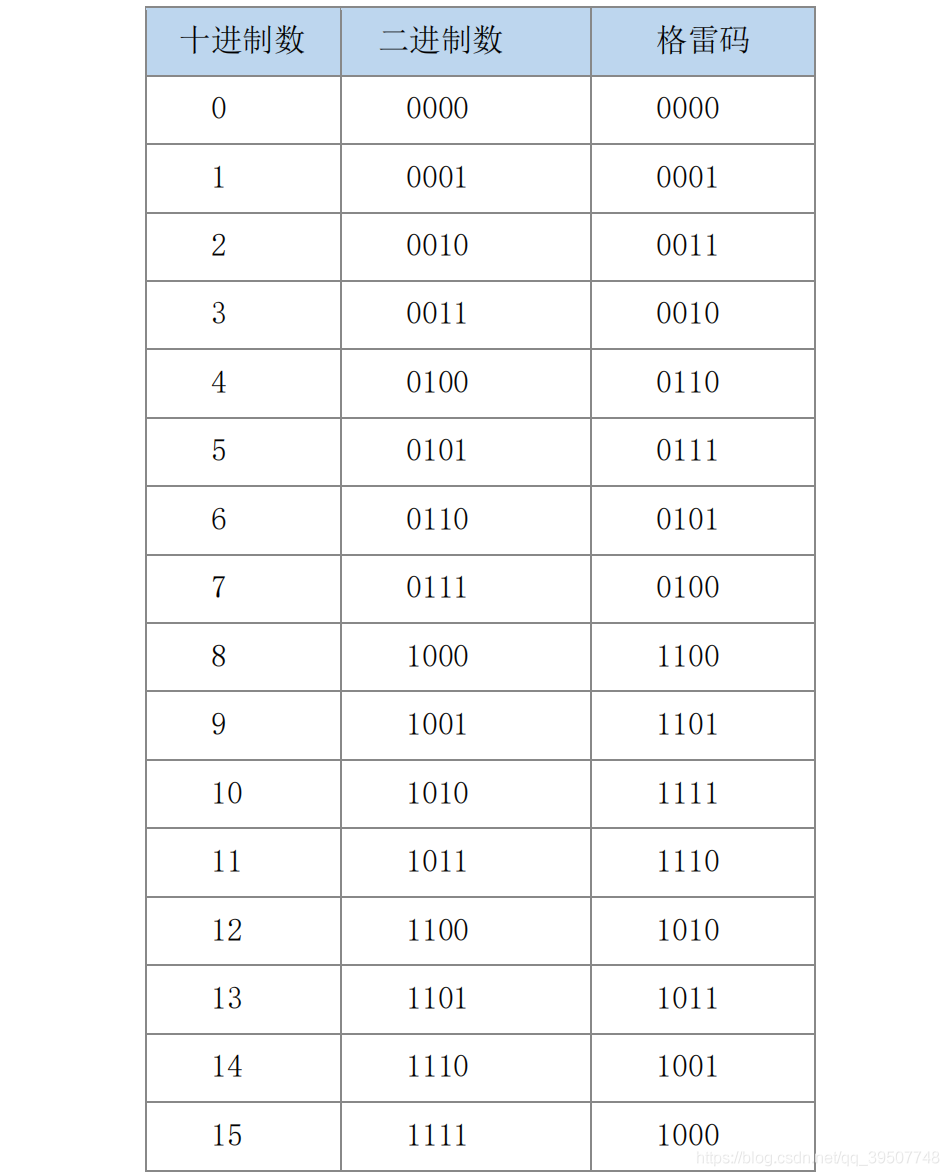

数制转换

其他进制转换成十进制:按位权相加即可。

十进制转换成其他进制:整数和小数部分要分别转换

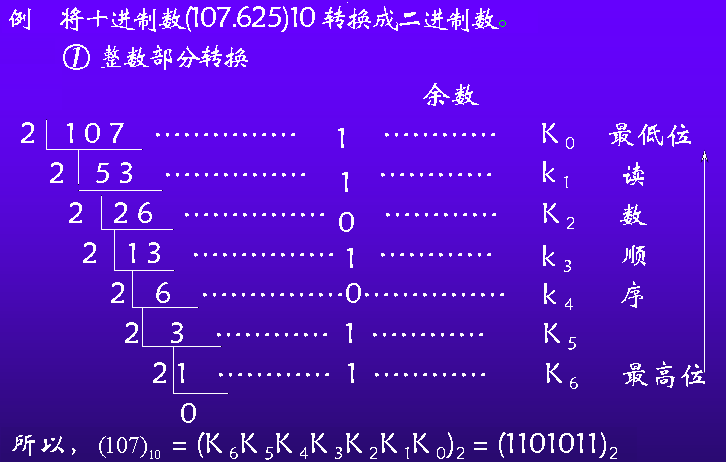

整数部分:

比如说十进制整数部分转换为N进制。那就用整数除N取余数,直到商为0。然后以从下到上的顺序取高位到低位。

比如说下面转换为二进制的。

小数部分:

假设从十进制小数部分转换为N进制。那就用乘N取整数部分,直到小数为0(或者达到精度要求)。然后从上到下的顺序,取从左到右的结果。

比如说:

转换完了之后整数部分和小数部分合并。

- 二进制/八进制/十六进制之间的转换

- 二进制转八进制:小数点起三位一组,整数部分不够三位向前添0,小数部分不够三位向后添0。

- 二进制转十六进制:从小数点起四位一组,整数部分不够四位的向前添0,小数部分不够的向后添0

- 八进制/十六进制转二进制:上面的逆过程。

- 八进制/十六进制转十六进制/八进制:先转换成二进制,然后再从二进制转换过去。

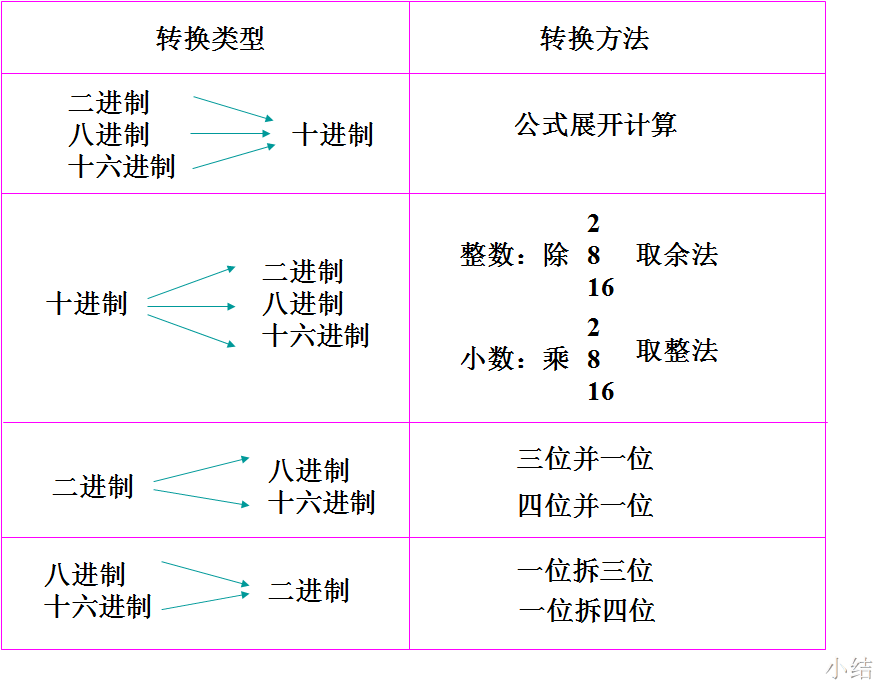

二进制编码

- 自然码:形式和二进制数相同。每位都固定权值。是有权码。

- 循环码:相邻的两个数码中,只能有一位数码不同。没有固定权值。是无权码。

- 格雷码:是运用比较频繁的一种循环码。如下:

- 格雷码:是运用比较频繁的一种循环码。如下:

- BCD码:是二十进制码。即二进制形式的十进制码。所以每四位最多表示到9。可以在尾部加上奇偶校验码。

例:十进制数转换为8421BCD码。即29020010 1001 0000 0010,每位数码分别转换。 - 余三码:属于BCD码。在8421码的基础上每个代码都加上0011得到。余三码也是无权码。

1.3 逻辑函数

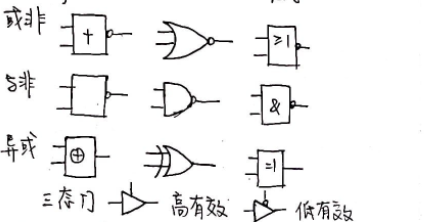

- 异或门只有两个输入端

(这里的高有效和低有效指的是三态门使能端是高有效还是低有效)- 同或就是”异或非“。逻辑图也是这么表示的。

- 分配律:

- 吸收律:

- 冗余律:

- 摩根定律

- 代入规则

- 反演规则:或换成与,与换成或。原变量换成非变量,非变量换成原变量。1换成0,0换成1。用于快速求F的非函数。

- 变换后保持原有的运算优先级,即先括号,再与,后或

- 不属于单个变量上的反号要保留

- 对偶规则:与换成或,或换成与,1换成0,0换成1。逻辑变量不作变换。若某个逻辑恒等式成立,则其对偶式也成立。

1.4 卡诺图

逻辑函数写作唯一的最小项表达式,如:

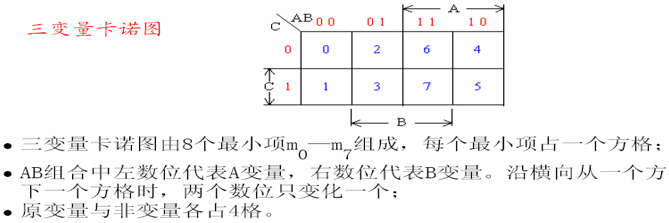

三变量卡诺图:

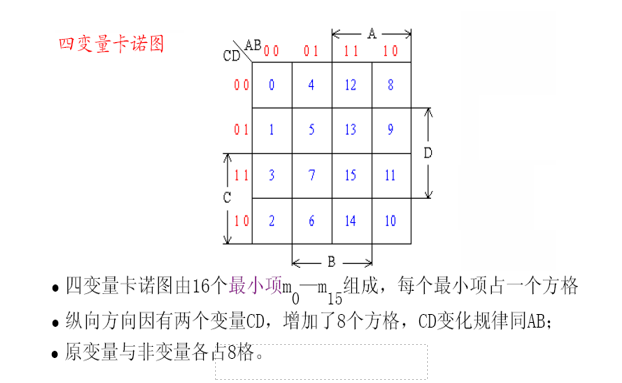

四变量卡诺图:

11写在10前面,这么写方便最小项合并。把卡诺图中逻辑相邻的最小项全都合并,就可以得到化简后的式子。化简结果不唯一。注意合并的数量只能是2的倍数。同一个最小项可以被包含多次。

无关项:无关项分为任意项和约束项,用

表示。

2.1 组合逻辑分析

阅读电路图

有使能端的时候要写出控制信号与F的真值表。

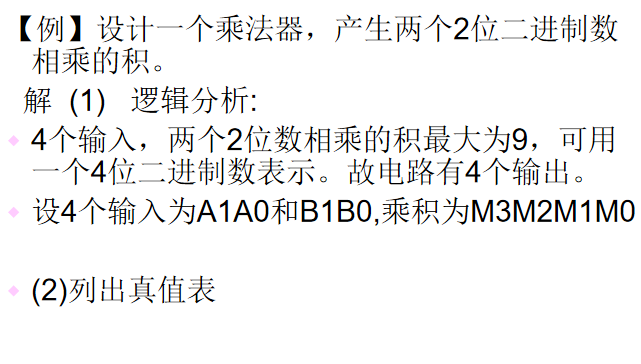

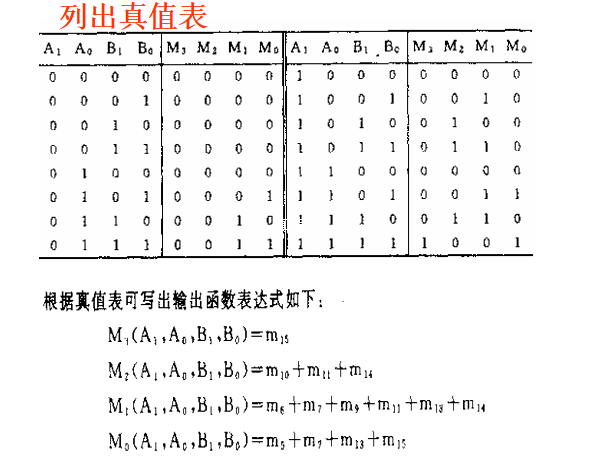

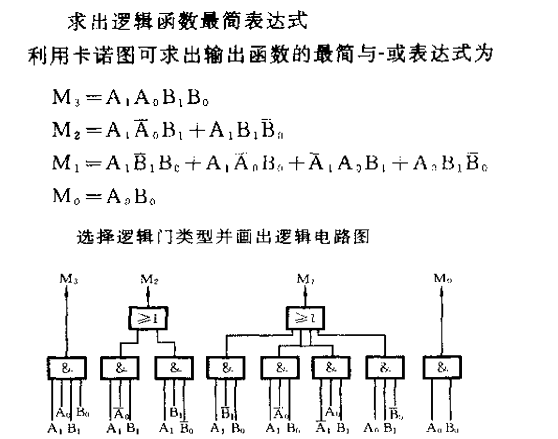

2.2 组合逻辑设计

分析因果关系

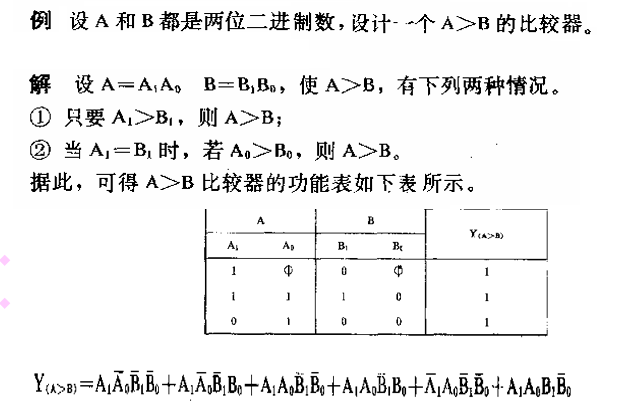

例1:

例2:

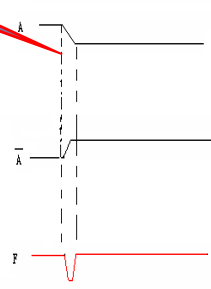

2.4 组合逻辑中的竞争冒险

电路表达式里,有俩互补输入信号(同时向相反状态变化)时,然后输出端可能有尖峰脉冲,就称为竞争冒险。

尖峰脉冲就是输出那条线突然刺楞了一下,冒出了一个小尖尖。

打个比方。

现在有

这个时候

波形图里头,

这产生尖峰脉冲的原因叫延迟(

还可能有个原因叫畸变,即波形失真:

明显没有延迟,但也有尖峰脉冲。

延迟和畸变都有,也有尖峰脉冲。

以上这一大堆估计都不考,要考的是下面的。

判断是否有尖峰脉冲

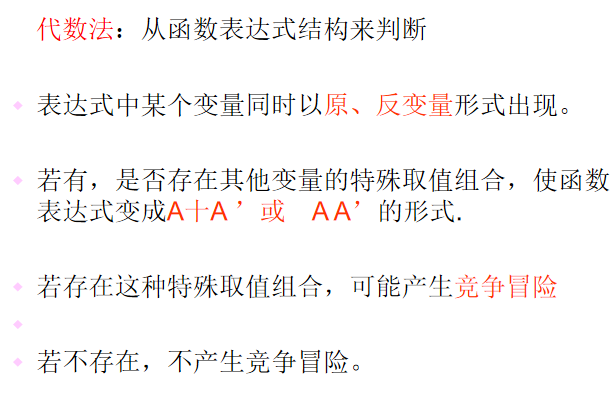

- 代数法:

- 卡诺图法:

- 消除竞争冒险措施

1.引入选通脉冲。

原理是输出稳定后才有选通脉冲,才可以输出,否则不产生选通脉冲,不允许输出。

2.接滤波电容。

滤波电容两端电压不能突变,消除干扰脉冲。

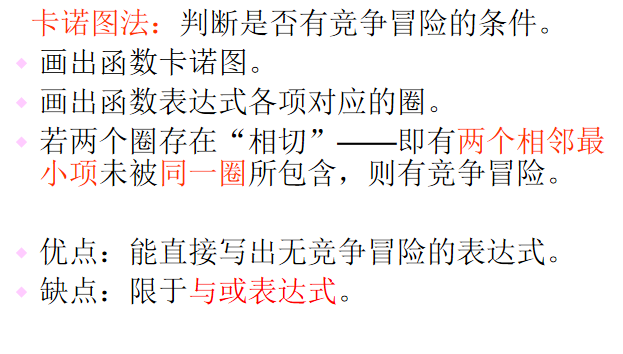

3.修改逻辑设计,增加冗余项。

就是卡诺图法的那个意思,找个圈把能包但没包的包起来。

2.5 常用规模组合逻辑电路标准构件

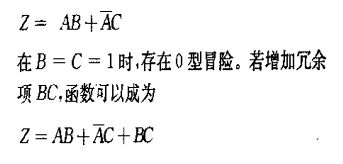

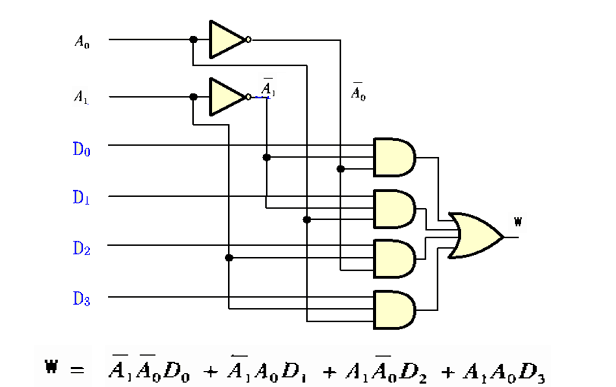

数据选择器(MUX)

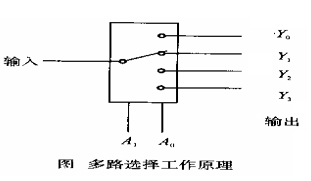

多路输入,单路输出

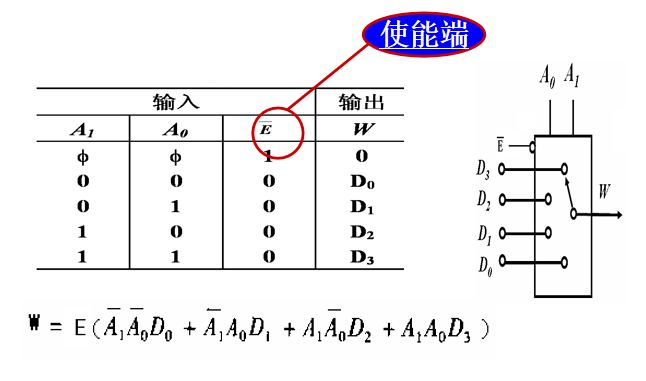

带使能端的MUX

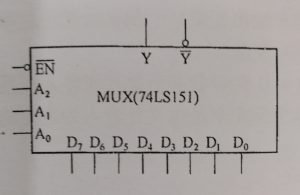

74lS153:双四选一 74LS151:八选一

这里给的图是151.

注意:

153的使能端工作方式和151的一致。

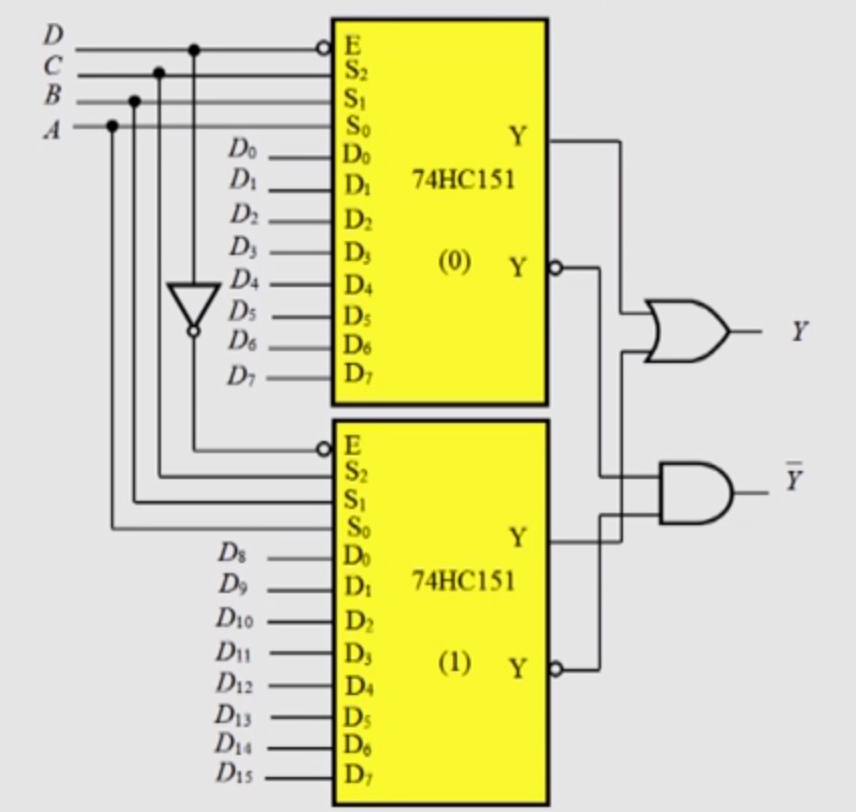

容量扩展:

四选一

实现方法:控制端的最高位控制使能端,低位正常输入,由此确定是高位片输出还是低位片输出。

如两个八选一构成十六选一:

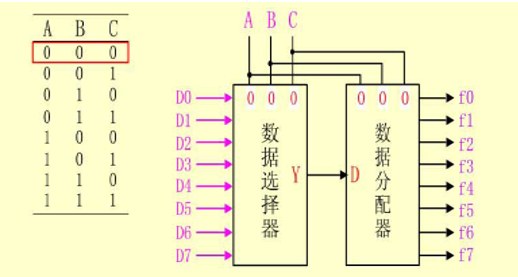

数据分配器(DMUX)

单路输入,多路输出

也称为1:4线数据分配器。

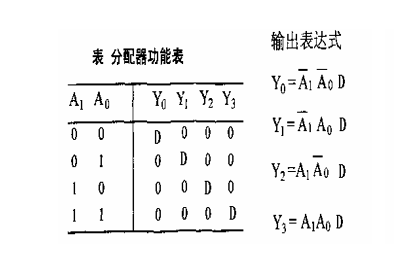

双1:4线数据分配器 74LS155

两个使能端都有效的时候,控制端输入

控制 的输出位置,如 ,数据 传输到 ,数据 传输到 使能端无效,对应的数据输入被封锁。

1D=2D,1ST=(2ST)’=A2的时候,变为1:8分配器。

容量扩展:

和选择器的思想基本一致,具体可以参考74LS155变为1:8分配器的例子。

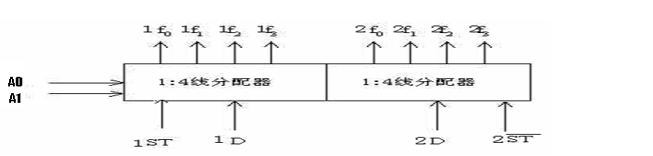

分时传输:

DMUX和MUX一起实现8路数据(分时)传输。

译码器

将输入的二进制码对应到某一位的输出。

分为两种,变量译码器和显示译码器。

- 变量译码器:2—4线译码器,3—8线译码器,4—16线译码器等。n种输入可以得到

个输出,每个输出端都对应一个最小项。让使能端E=D可以达到数据分配器的效果。

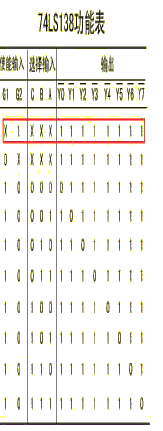

74LS138 3—8译码器

- 输出端

是低电平有效,比较特殊。并不是说译码器的输出都是低电平有效。比如说ppt的2—4译码器输出仍旧是高电平有效。 - 使能端有两个部分组成,

,其中 由 组成。正常工作时, 的时候有效。具体如图:

双2:4译码器 74LS139

- 输出是低电平有效,和138一致。

- 使能端依旧是

的时候可以正常工作。即低电平有效。

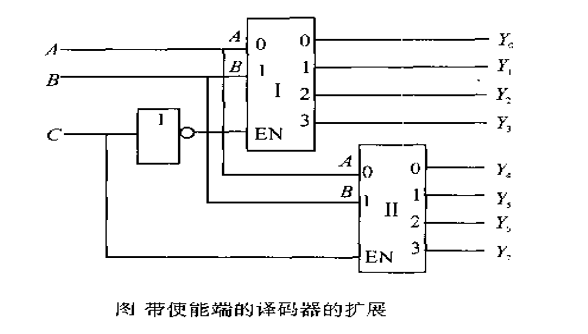

译码器扩展:

思路还是跟选择器一样。

注意图里给的不是139.

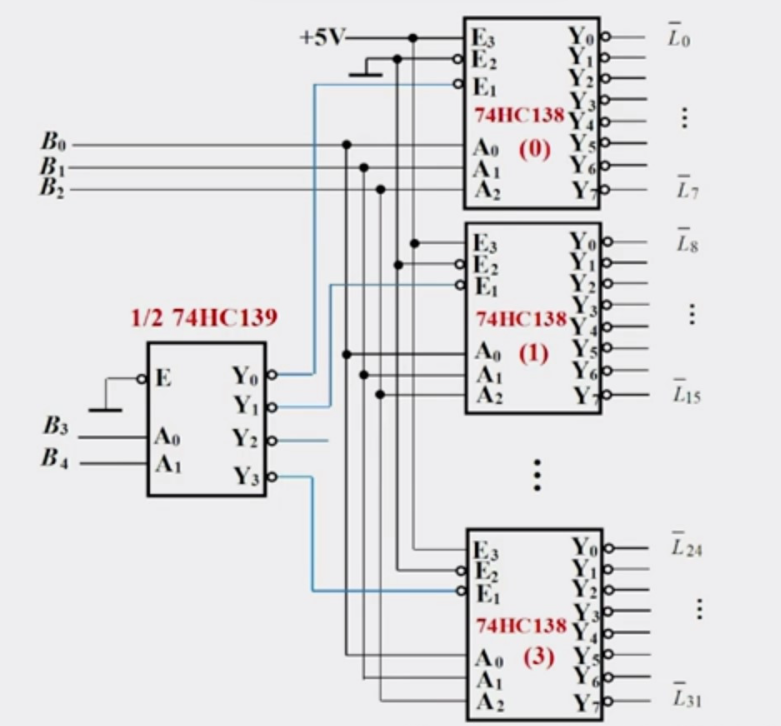

用139和138构建5:32译码器:

本质上还是用使能端进行选择。

- 显示译码器:实现十进制的表达的译码器。

二-十进制码(BCD码)

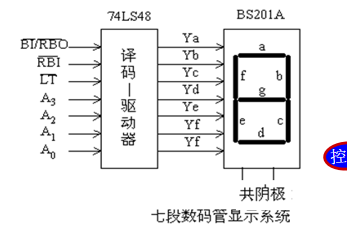

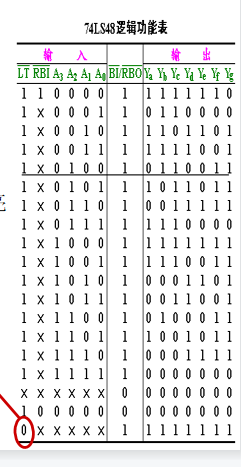

显示译码器 74LS48(共阴极)

用4选1数据选择器构建16选1数据选择器

使用译码器作为使能端的选择部分:

这里的用的是138,用139也行,原理一样。

如图:

逻辑实现:

是熄灭信号, 的时候 都为0。 优先级很低,要其他的全部满足特定条件( )才有效。 是试灯信号, 的时候,七段亮。优先级仅次于

真值表:

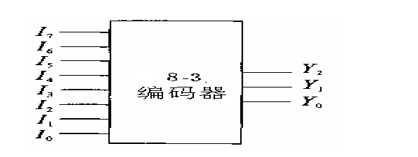

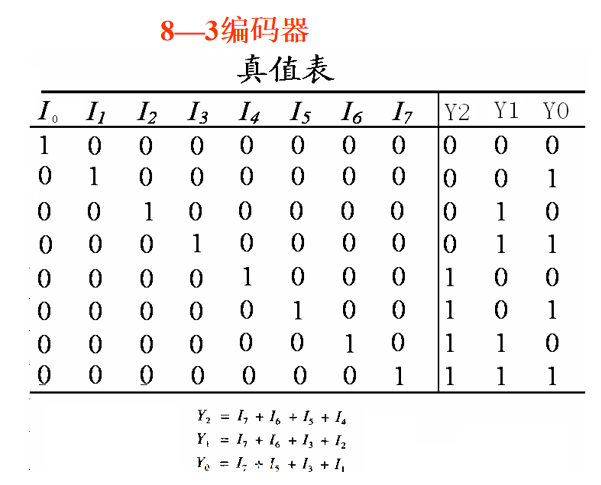

编码器

对输入的某一位的输出转换成对应的二进制编码。

只能有一个输入端有效,否则输出无效。

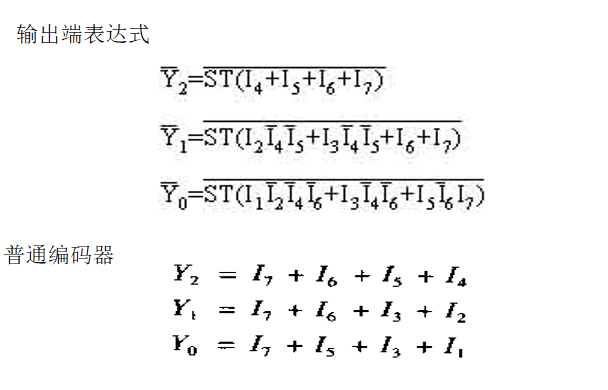

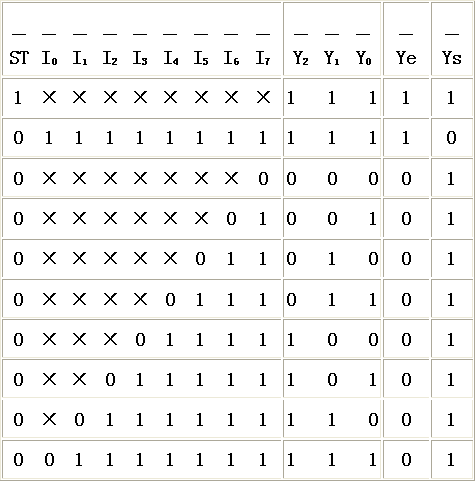

8-3优先编码器 74LS148

- 允许多个输入信号同时有效。

- 只对优先级最高的输入信号进行编码。

- I7优先级最高,I0最低。

- 简易真值表如下(ST=1,编码器工作)

- 148的使能端有两个,

,单独使用是以 为准。而扩容的时候两个都要用上。(参考教材p54,高位 接低位 ) - 输出端表达式和普通编码器的区别:

- 注意:

输入的是,输入也是反相的,只有对应输入的 才视为是有效输入。

输出的是,输出是反相的。

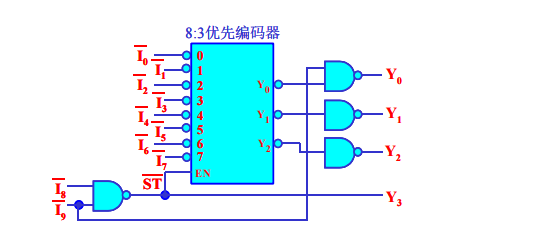

BCD(二-十进制)优先编码器 74LS147

一片148和与非门实现8421BCD优先编码

如图:

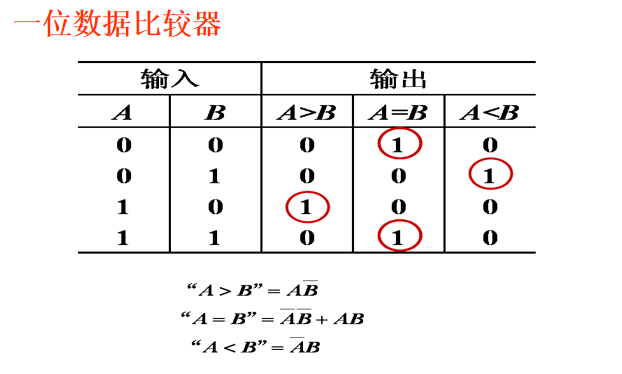

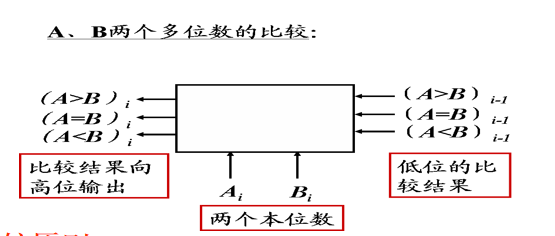

数据比较器

完成两个二进制数码大小比较。

真值表及相应含义:

记一下大于等于小于对应的逻辑表达式。

含有输入进位的

原则:

1.本位值大(小)。输出大于(小于)

2.本位相等,按输入的进位结果输出。

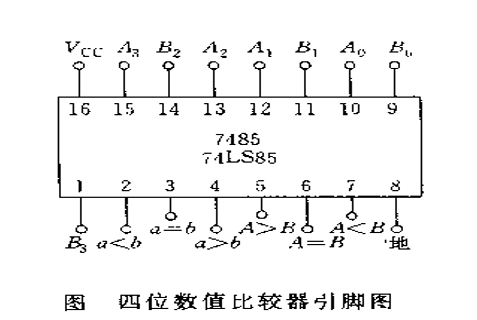

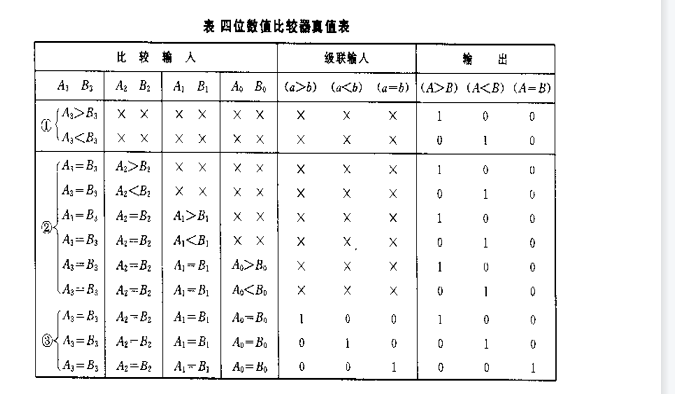

四位比较器 74LS85

对应的真值表:

如果一共就只有四位数的比较,那么

从4位扩展为更高位的时候,低位输出接高位的级联输入。

加法器

实现二进制数加法运算。

按是否考虑低位信号,分为半加器(不考虑)和全加器(考虑)。

按进位信号的产生方法,分为串行加法器和并行加法器。

一位加法半加器

S是和数,C是进位信号一位加法全加器

串行加法器

三个输入(加数,被加数 ,低位进位信号 )

两个输出(和数,高位进位信号 ) 特点在于每次只能算一位,要算更高位数只能向上递推。

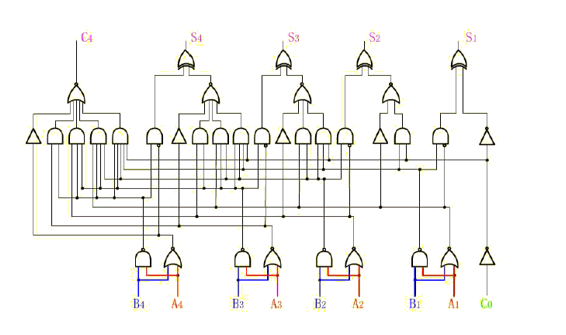

并行加法器

特点是可以一次性算完所有位数。但会导致位数越高,其逻辑表达式越复杂。

即逻辑表达式里直接用对应低位的进位表达式替换掉低位的进位,直到替换到只有输入的位。

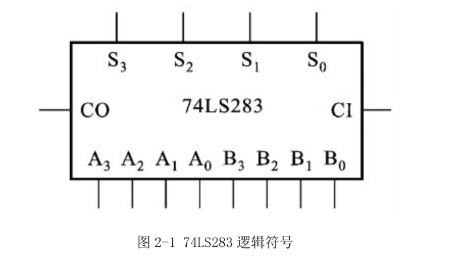

四位二进制超前进位全加器 74LS283

可以实现四位二进制数的全加操作。

如图:

级联的操作和一位全加器串行级联是一样的。

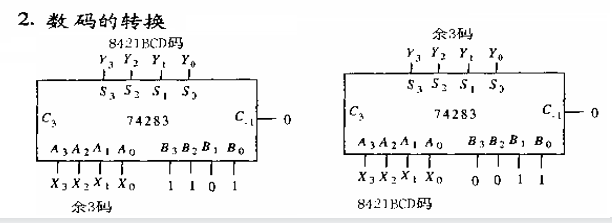

283实现数码转换

这里给的转换是BCD码和余3码之间的转换。

其中余3转BCD码是加1101(13),BCD转余3码是加0011(3)

如果是从二进制自然码转换:

1.BCD码:判9/有进位

2.余3码:+3

奇偶校验器

校验传送过程中是否误传。

对传送得到的信息码产生对应的监督码。分为奇校验和偶校验。

8位奇偶发生器 74LS280

奇校验。

- 监督码Fod满足:

则如果八位信息码里的1为奇数,那么Fod=0,如果是偶数Fod=1. - 接收码Fev满足(Fev表达式和Fod一致):

接受的传输码中的1为奇数,Fev=0,传送正确。

接受的传输码中的1为偶数,Fev=1,传输错误。

第三章 时序逻辑

时序电路:组合电路和存储电路

同步时序:电路中的记忆元件统一受公共CP控制。

异步时序:没有公共的CP信号,各个记忆元件不受同一个CP控制。

3.1 锁存器

按照逻辑功能:SR,D锁存器。

按照电路结构:基本锁存器,门控锁存器(有使能端)。

根据输出是否有非门,锁存器也分为低电平有效和高电平有效。做题的时候要看清楚。

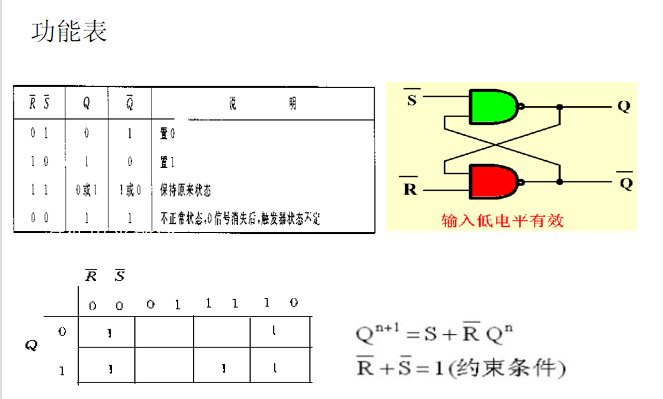

SR锁存器

特性方程:

后面那个式子是约束条件。

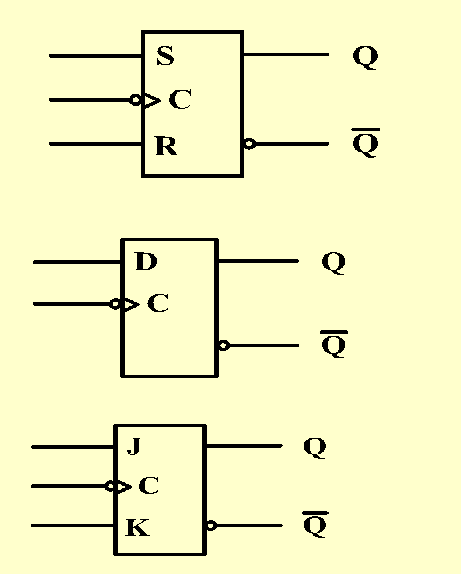

逻辑图和功能表如下:

注意SR锁存器输入的是

只有

SR锁存器是低电平敏感,由于输入的是

门控SR锁存器:

增加了一个使能端EN。

只有在EN=1的时候,才会接受SR的变化信号。否则状态保持不变。

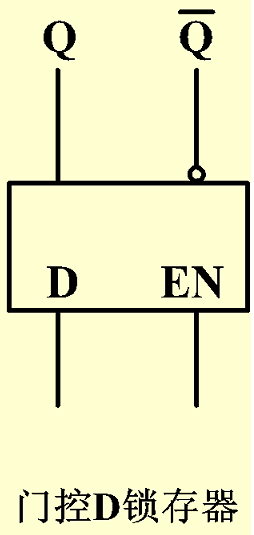

门控D锁存器 74LS373

SR门控锁存器的变体。相当于用

使能端EN不做变化。

D=1,EN=1,锁存器置1,

D=0且EN=1,锁存器置0.

EN=0,状态不变。

图这么画:

3.2 触发器

按照有无时钟信号:同步触发器和异步触发器

注意画法

C前面的三角代表是按照时钟信号边沿方式工作,

三角前的有圆圈代表时钟信号负脉冲(下降沿触发)

没有就代表正脉冲(上升沿触发)

SR触发器

激励方程和真值表和SR锁存器一致。唯一的区别是在时钟信号的上升沿触发,即CLK从0到1的时候。(有时候也可能是下降沿触发,看图怎么画)

D触发器

同D锁存器。上升/下降沿触发。

JK触发器

特性方程:

JK=00 保持

JK=01 置0

JK=10 置1

JK=11 翻转

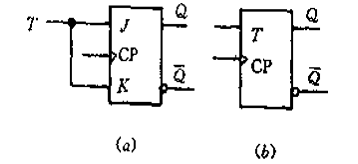

T触发器

是JK触发器的变体。和SR改D不同,JK改T不需要非门,直接用T替换J和K即可。

得到的表达式为:

功能表:

T=0 保持

T=1 反转

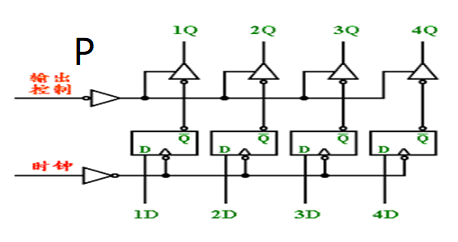

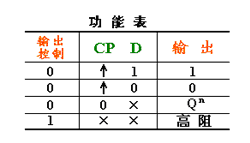

3.3 寄存器 移位寄存器

寄存器:由

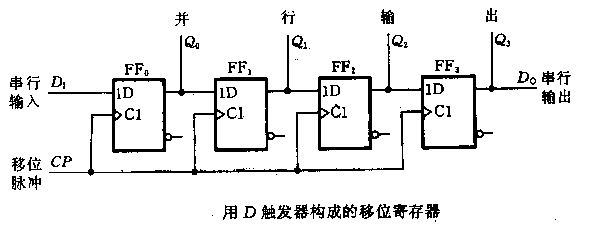

下图是用D触发器构成的寄存器:

CP是时钟信号

P是输出控制信号

iD是输入数据

Q是寄存数据

iQ是输出数据

图里采用的是时钟脉冲负边沿触发。数据iD在时钟脉冲的负边沿被送到D触发器。然后输出控制信号来决定是否将Q输出得到iQ。

输出控制信号低电平有效,高电平阻止。

所以真值表:

移位寄存器

分为左移寄存器,右移寄存器,双向移位寄存器

具有左移,右移和并行置数功能的寄存器叫通用移位寄存器。

右移寄存器图示:

如果将其看作是对一个二进制数(从右至左是从低位到高位)的操作,那么右移一位相当于是:

其中

左移寄存器就是反向来接。不放图了。

同样的,如果看作二进制数,那么左移一位相当于是

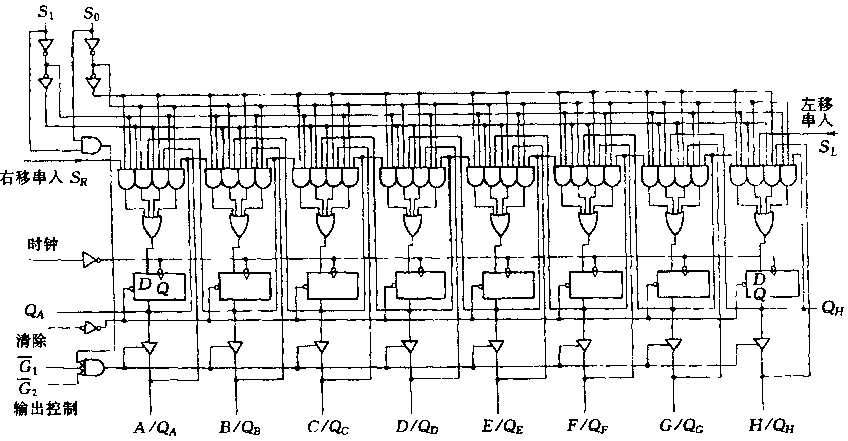

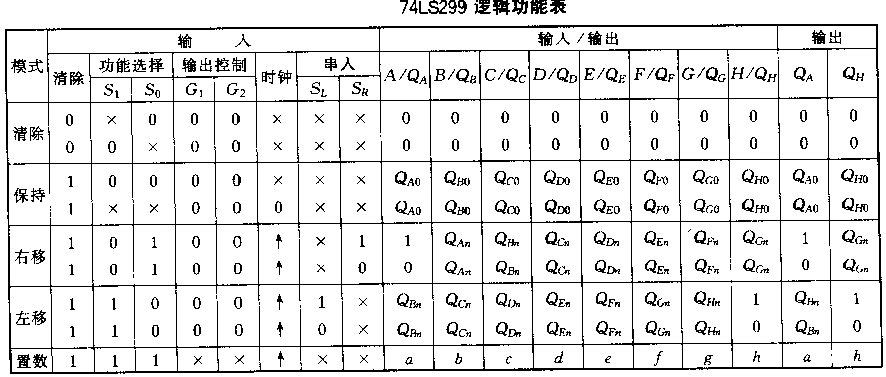

八位通用移位寄存器74LS299

这玩意儿比较复杂。

功能控制端S1,S0:决定四种工作状态

S1 S0 = 11:

同步并行置数::三态输出处于高阻态,不能输出。时钟脉冲把输入/输出线的数据装入寄存器。

S1 S0 = 00:

保持模式::这个模式下不做其他工作。只要输出控制是有效,那就可以读出寄存器。

S1 S0 = 01:

右移模式::通过时钟脉冲和右移串入实现数据右移。

S1 S0 = 10:

左移模式::通过时钟脉冲和左移串入实现数据左移。

输出控制端G1‘,G2’:任何模式,只要输出控制有效,那寄存器就读出。

清除端:低电平时将寄存器清0。

输入/输出三态门:输入关闭,输出打开

时钟端:上升沿实现左移,右移,置数等操作。

左(串)输入端SR(SL)

并行置数是利用三态门,并行地将数据从三态门装入寄存器中。对应的是数据

。输出的时候对应的是

功能表:

3.4 计数器

一般是在移位寄存器的基础上得到的,通过最后的寄存器对最开始的寄存器施加反馈。

- 对输入脉冲进行计数或者记忆的逻辑器件。

- 输入脉冲改变电路状态。状态图是一个有限环

- 计数器记忆状态的最大数目被称为模

同步计数器:触发器共用同一个计数脉冲CP,触发器处于同步工作的模式

异步计数器:不是同一个计数脉冲CP,触发器的状态变化有先后差别。

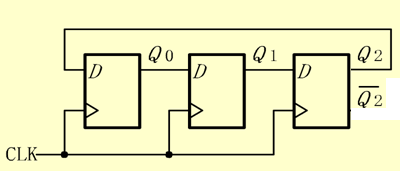

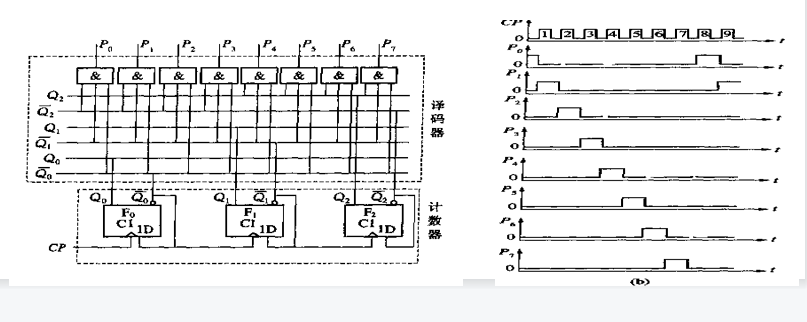

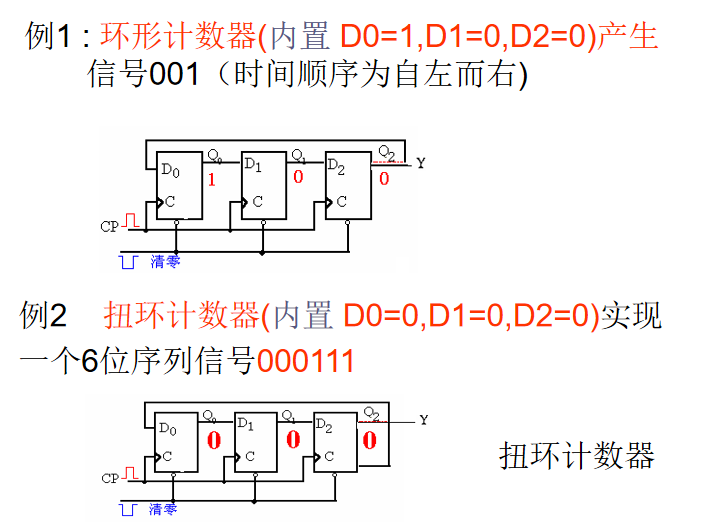

环形计数器(最后反馈的是

)

如图:

对于n个寄存器,可以构成模m=n的环形计数器。没有自启动能力(如000)。

扭环计数器(反馈的是

)

如图:

对于n个寄存器,可以构成模m=2n的计数器。无自启动能力(如101)。

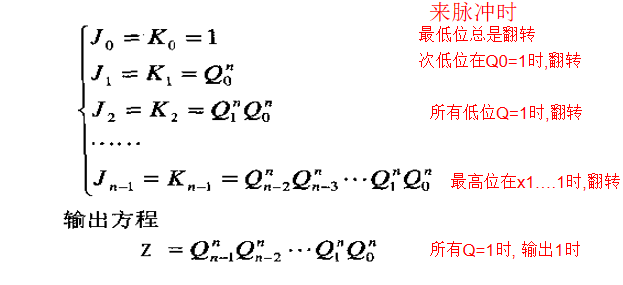

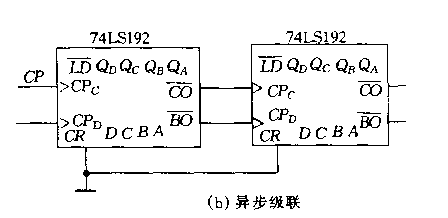

二进制同步加法计数器

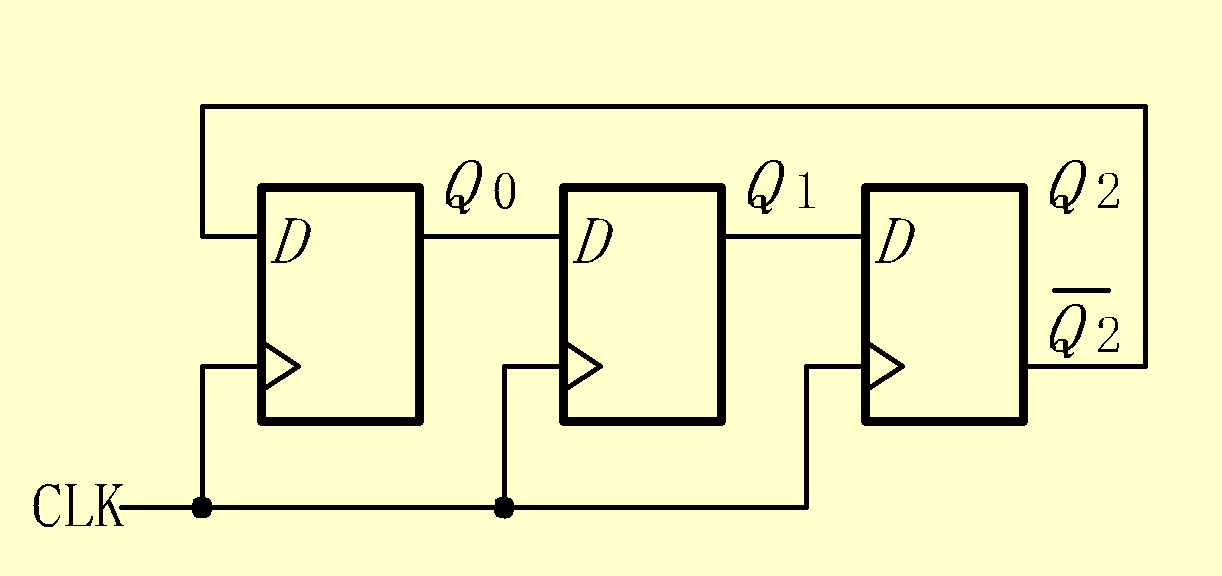

使用JK触发器实现n位二进制同步加法计数器,如图:

触发器数目为n,模M=。

理解的重点在于翻转的条件。可以理解为是用所有低位Q全部与之后作为T。构成了T触发器。从而来得到翻转需求。

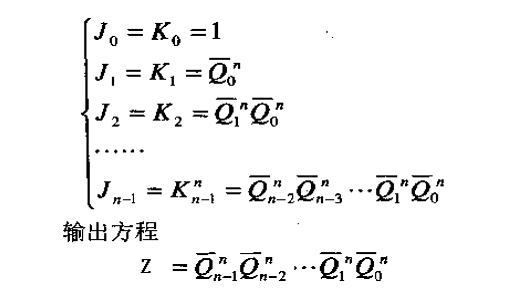

二进制同步减法计数器

同样用JK触发器实现,如图:

就是把加法计数器的反过来。

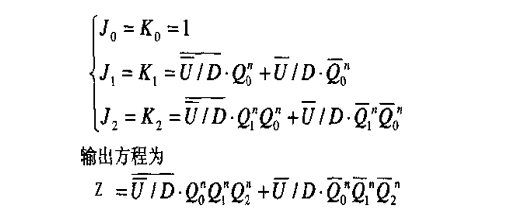

二进制可逆计数器

本质上就是把加法和减法结合起来,然后给一个加/减控制信号。这样就得到了同步可逆计数器。 =0作加法计数。 =1作减法计数。 之后再让加减法的驱动方程分别和有效控制信号相与之后再相加,就可以得到可逆计数器驱动方程。

比如说3位二进制同步可逆计数器的驱动方程如下:

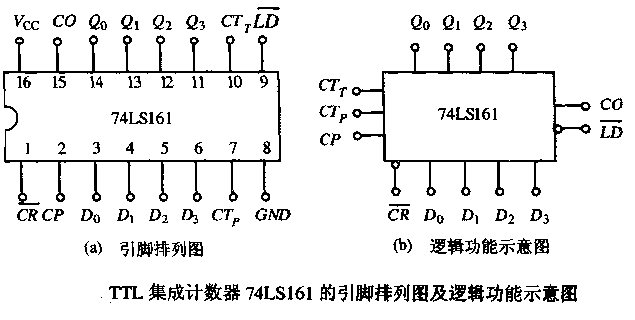

集成4位二进制同步加法计数器74LS161

图如下:

异步清零:

并行置数:

加法计数:

保持功能:

异步计数器

我不知道。

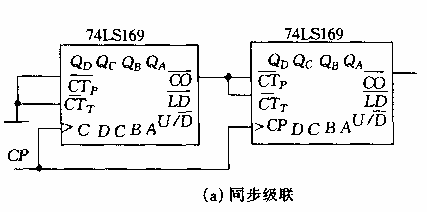

计数器级联

注意级联之后,得到的新的计数器的模是级联计数器模之和。

同步级联:

- 时钟接到各计数器时钟的输入(计数器同步工作)

- 前级计数器的进位CO作为输出接入后级计数器的控制端。只有进位信号有效,后级计数器才可以工作。

如图:

异步级联:

- 前级计数器的输出作为后一级计数器的时钟信号

如:两片双时钟十进制可逆计数器74LS192构成M=100的可逆计数器:

:加计数时钟输入 :减计数始终输入 :复位端。高电平有效。 :进位输出,1001时负脉冲输出 :借位输出,0000时负脉冲输出。

- 前级计数器的输出作为后一级计数器的时钟信号

预置法构成任意进制计数器

用模N计数器实现模M的计数器

- 用预置端让模N从预置状态

开始工作,到达 ,共M个状态。 - 到达终止状态时产生预置信号(LD=0),将预置状态重新打入计数器。实现M进制的计数。

- 条件:

状态有效。

以上是同步预置时的情况,异步预置有所不同。

由于异步计数时,最后的终止状态

上面的是构成加法计数器的方法,如果是减法计数器,那预置状态分别是

复位法构成任意进制计数器

这个要求有复位端(

- 计数器从0开始计数。到达M-1状态,产生一个复位信号

- 将复位信号加到计数器的复位端,让计数器清零。实现M进制计数。

计数器的应用

- 分频器。

把输入脉冲的频率降低,就说是分频,降低到几分之一就是几分频脉冲。

这个用二进制计数器可以完成。

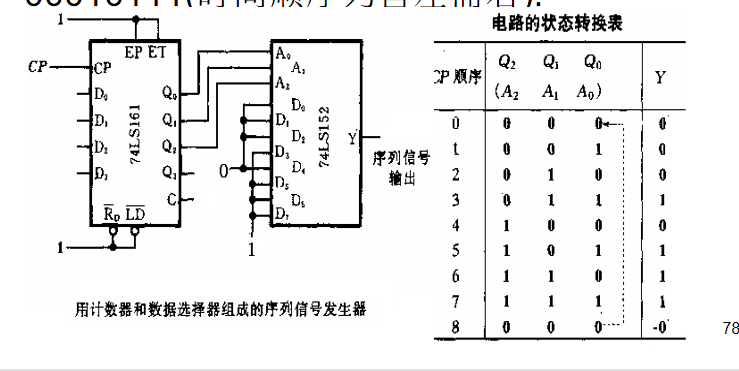

- 数字序列发生器

将不同节拍的脉冲分配到指定的输出。

译码器和计数器构成。

N位计数器就有个状态。 - 脉冲分配器

计数器和数据选择器实现序列信号发生器。

如:

常用器件总结

74LS153:双四选一数据选择器

74LS151:八选一数据选择器

74LS155:双4:1数据分配器

74LS138:3:8译码器

74LS139:2:4译码器

74LS48:共阴极显示译码器

74LS148:8:3优先编码器

74LS147:BCD二-十进制优先编码器

74LS85:四位比较器

74LS283:四位二进制超前进位全加器

74LS280:8位奇偶发生器

74LS373:门控D锁存器

74LS299:八位通用移位寄存器

74LS161:集成4位二进制同步加法计数器

74LS163:同步4位二进制加法计数器,M=16,cp上升沿触发

时序电路设计

米里型:输出信号取决于电路输入和存储状态

穆尔型:输出信号仅取决于电路状态,而与电路输入无关